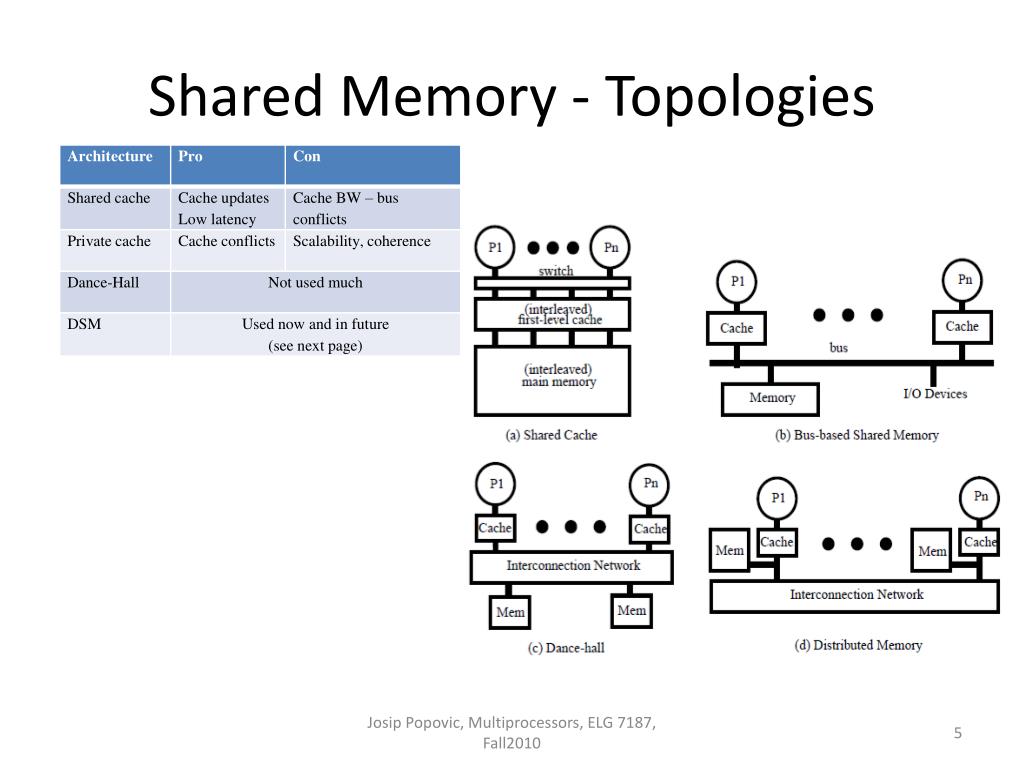

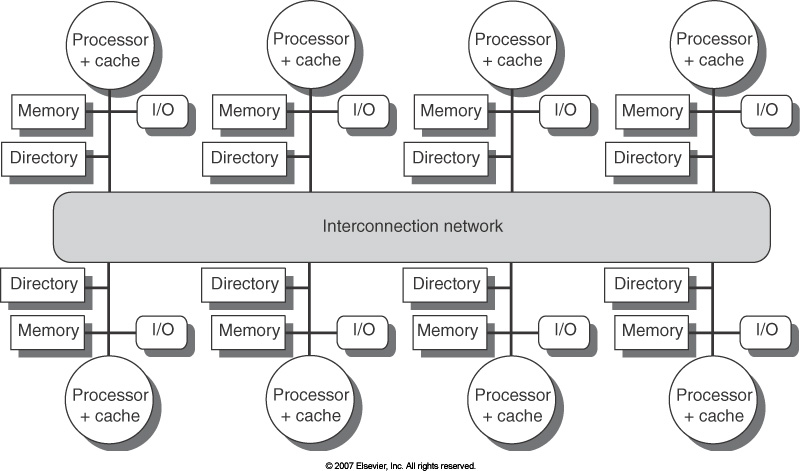

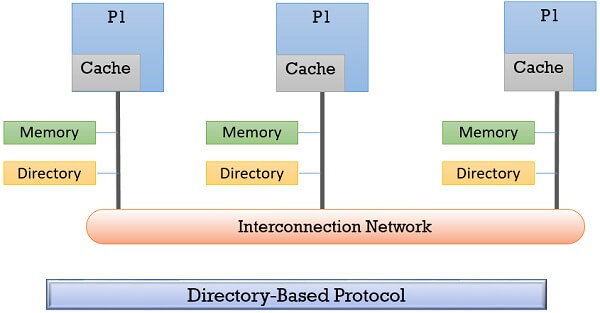

In such systems, each processor or core typically has its own cache memory to improve performance. In this case, concurrent tag lookups are only possible when the state of the block in the cache does not change as a result of the snoop action.Back to Glossary Introduction to Cache CoherenceĬache coherence refers to the consistency and synchronization of data stored in different caches within a multiprocessor or multicore system. (b) Determine how long it takes to carry out the memory requests from each individual processor under the assumption that we duplicate the tag directory to allow concurrency between inbound snoop actions and outgoing processor read/write generated protocol actions. (a) Determine how long it takes to carry out all memory requests under the assumption that snoop actions get a higher priority than processor read/write requests from that same unit they have to wait until the snoop action is done. This action consists of transferring the request on the bus and making a snoop action in each cache the time for the latter is also shown in Table 5.6.ĭetermine for each of the cases below how long it takes to carry out the following sequence of reads and writes to blocks and, where the notation and means a read and write operation, respectively, by processor/cache unit to block B.

#CACHE COHERENCE IN SHARED MEMORY MULTIPROCESSOR UPGRADE#

A bus upgrade request takes less time as it does not involve a block transfer but rather invalidates other shared copies.

While a read and write hit take only a single cycle, a read request takes 40 cycles as it has to bring the block from the next level of the cache hierarchy.

The time it takes to carry out various protocol actions is listed in Table 5.6. What makes the MOESI protocol beneficial and what would remove the performance advantage of MOESI over MESI?Īssume that a shared-memory multiprocessor using private caches connected to a shared bus uses an MSI cache protocol to maintain cache coherence. (c) Compare the access cost and traffic of MESI in Problem 5.5 with your findings for MOESI in this exercise. (b) Compare the traffic generated by the MSI and MOESI protocols counted in bytes transferred using the data in Table 5.6, and assuming that B is 32 bytes. MOESI, assuming the access costs for the protocol transactions to be as in Table 5.6? (a) How many cycles does it take to execute the access sequence under MSI vs. Consider the following sequence of accesses by the processors: We want to determine the time and traffic under the execution of a sequence of accesses with an MSI and with a MOESI protocol by using the parameters in Table 5.6. Our baseline cache coherence protocol is an MSI protocol, but we want to investigate what performance gain can be achieved by adding an Ownership state to make it a MOESI protocol according to Section 5.4.3.

Assume a shared-memory multiprocessor with a number of processor/private cache units connected by a shared single-transaction bus.

0 kommentar(er)

0 kommentar(er)